eXamen.press

**eXamen.press** ist eine Reihe, die Theorie und Praxis aus allen Bereichen der Informatik für die Hochschulausbildung vermittelt.

# Peter Marwedel

# Eingebettete Systeme

Übersetzt aus dem Englischen von Lars Wehmeyer

Peter Marwedel Fakultät für Informatik Technische Universität Dortmund Otto-Hahn-Str. 16 44221 Dortmund peter.marwedel@tu-dortmund.de

Übersetzer

Lars Wehmeyer

korrigierter Nachdruck 2008

ISBN 978-3-540-34048-5

e-ISBN 978-3-540-34049-2

DOI 10.1007/978-3-540-34049-2

ISSN 1614-5216

Bibliografische Information der Deutschen Nationalbibliothek Die Deutsche Bibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über http://dnb.d-nb.de abrufbar.

© 2008 Springer-Verlag Berlin Heidelberg

Dieses Werk ist urheberrechtlich geschützt. Die dadurch begründeten Rechte, insbesondere die der Übersetzung, des Nachdrucks, des Vortrags, der Entnahme von Abbildungen und Tabellen, der Funksendung, der Mikroverfilmung oder der Vervielfältigung auf anderen Wegen und der Speicherung in Datenverarbeitungsanlagen, bleiben, auch bei nur auszugsweiser Verwertung, vorbehalten. Eine Vervielfältigung dieses Werkes oder von Teilen dieses Werkes ist auch im Einzelfall nur in den Grenzen der gesetzlichen Bestimmungen des Urheberrechtsgesetzes der Bundesrepublik Deutschland vom 9. September 1965 in der jeweils geltenden Fassung zulässig. Sie ist grundsätzlich vergütungspflichtig. Zuwiderhandlungen unterliegen den Strafbestimmungen des Urheberrechtsgesetzes.

Die Wiedergabe von Gebrauchsnamen, Handelsnamen, Warenbezeichnungen usw. in diesem Werk berechtigt auch ohne besondere Kennzeichnung nicht zu der Annahme, dass solche Namen im Sinne der Warenzeichen- und Markenschutz-Gesetzgebung als frei zu betrachten wären und daher von jedermann benutzt werden dürften.

Einbandgestaltung: KünkelLopka Werbeagentur, Heidelberg

Gedruckt auf säurefreiem Papier

987654321

springer.com

#### Vorwort

## Relevanz eingebetteter Systeme

Eingebettete Systeme können definiert werden als informationsverarbeitende Systeme, die in ein umgebendes Produkt wie z.B. Autos, Telekommunikationsgeräte oder Produktionsmaschinen eingebettet sind. Solche Systeme haben viele gemeinsame Charakteristiken, u.a. das Einhalten von Zeitbedingungen, Zuverlässigkeit und Effizienz. Die Technologie eingebetteter Systeme ist eine Grundvoraussetzung, um das Paradigma der allgegenwärtigen Information (ubiquitous information) zu gewährleisten – eines der Hauptziele der modernen Informationstechnik (IT).

Nach dem Erfolg der IT im Bereich der Büroanwendungen und Geschäftsprozesse werden eingebettete Systeme in den kommenden Jahren das wichtigste Anwendungsgebiet für Informationstechnik sein. Aufgrund dieser Erwartungen wurde bereits der Begriff Post-PC Era geprägt. Dieser Begriff drückt aus, dass Standard-PCs in Zukunft weniger dominant sein werden. Prozessoren und Sofware werden zunehmend in viel kleineren Systemen verwendet werden, und in vielen Fällen werden sie sogar völlig unsichtbar sein, was zum Begriff des verschwindenden Computers geführt hat. Es ist heute bereits offensichtlich, dass technische Produkte sehr hochentwickelt sein müssen, um das Interesse der Kunden zu wecken. Autos, Kameras, Fernseher, Handys usw. lassen sich heute ohne clevere integrierte Softwarelösungen kaum noch verkaufen. Bereits heute übersteigt die Anzahl von Prozessoren in eingebetteten Systemen die Anzahl von Prozessoren, die in PCs verbaut sind – und dieser Trend wird sich weiter fortsetzen. Nach aktuellen Vorhersagen wird die Größe und Komplexität eingebetteter Software in den kommenden Jahren sehr stark wachsen. Es gibt auf diesem Gebiet eine neue Form des "Mooreschen Gesetzes": In vielen Produkten im Bereich der Konsumelektronik verdoppelt sich die Größe der Software alle zwei Jahre [Vaandrager, 1998].

Diese Relevanz eingebetteter Systeme wird in den aktuellen Studienplänen nicht ausreichend berücksichtigt. Dieses Buch soll dazu beitragen, die Situation zu verbessern. Es stellt Materialien für einen einführenden Kurs zu eingebetteten Systemen zur Verfügung, kann aber auch außerhalb von Vorlesungen eingesetzt werden.

## Zielgruppe dieses Buches

Dieses Buch wurde für die folgenden Leser konzipiert:

- Informatik-, Ingenieur-Informatik- und Elektrotechnik-Studenten, die sich im Bereich der eingebetteten Systeme spezialisieren wollen. Das Buch ist geeignet für Studierende ab dem dritten Studienjahr, die bereits ein grundlegendes Verständnis von Rechner-Hard- und Software haben. Es ebnet den Weg zu fortgeschrittenen Themen, die in Folgekursen vertieft werden sollten.

- Ingenieure, die bislang im Bereich der Hardware für Rechensysteme gearbeitet haben und die sich intensiver mit dem Bereich der Software für eingebettete Systeme beschäftigen wollen. Dieses Buch sollte ein ausreichendes Hintergrundwissen zur Verfügung stellen, um aktuelle relevante Publikationen auf dem Gebiet zu verstehen.

- Professoren, die einen Studiengang oder eine Studienrichtung für eingebettete Systeme konzipieren.

# Eingliederung eingebetteter Systeme in einen Studienplan

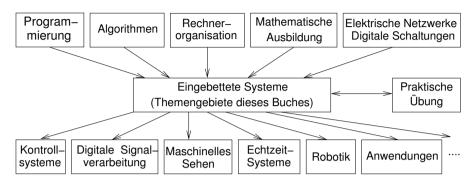

Dieses Buch setzt Grundwissen in den folgenden Gebieten voraus (s. Abb. 0.1);

- Elektrische Schaltnetze auf Oberstufen-Niveau (z.B. Kirchhoffsche Gesetze),

- Operationsverstärker (optional),

- Rechner-Hardware, z.B. anhand des einführenden Buches von J.L. Hennessy und D.A. Patterson [Hennessy und Patterson, 1995],

- Grundwissen digitaler Schaltungen wie etwa Gatter und Register,

- Programmierung,

- Endliche Automaten,

- Fundamentale mathematische Konzepte wie Tupel, Integrale und lineare Gleichungssysteme, möglichst auch die Grundlagen der Wahrscheinlichkeitstheorie.

- Algorithmen (Graphenalgorithmen und Optimierungsalgorithmen wie z.B. Branch-and-Bound),

- NP-Vollständigkeit und Berechenbarkeit.

Abb. 0.1. Positionierung der Themen dieses Buches

Eines der Hauptziele dieses Buches ist es, einen Überblick über den Entwurf eingebetteter Systeme zu geben und die wichtigsten Themen im Bereich der eingebetteten Systeme zueinander in Beziehung zu setzen. Es soll sowohl Studierende als auch Lehrende dazu motivieren, sich weitere Themen zu erarbeiten. Einige Themen werden in diesem Buch erschöpfend behandelt, andere nur kurz angerissen. Diese kürzeren Abschnitte sollen helfen, verwandte Themengebiete in den Gesamtkontext einordnen zu können. Dadurch können Lehrende entsprechend ihrer eigenen Vorlieben Zusatzmaterial in den Kurs einbauen. Das Buch sollte durch weiterführende Kurse ergänzt werden, die vertiefendes Wissen in den folgenden Themengebieten vermitteln:

- Digitale Signalverarbeitung,

- Robotik,

- Maschinelles Sehen,

- Sensoren und Aktuatoren,

- Echtzeitsysteme, Echtzeitbetriebssysteme und Echtzeit-Scheduling,

- Regelungstechnik,

- Spezifikationssprachen für eingebettete Systeme,

- Rechnergestützte Entwurfsumgebungen für applikationsspezifische Hardware,

- Formale Verifikation von Hardware,

- Systematisches Testen von Hardware und Software,

- Leistungsbewertung von Rechensystemen,

- Entwurfsmethoden für energiesparende Systeme,

- Sicherheit und Verlässlichkeit von Computersystemen,

- Ubiquitous Computing (allgegenwärtiges Rechnen),

- Anwendungsgebiete in der Telekommunikation, im Automobilbereich, in medizinischen Geräten und intelligenten Häusern,

- Konsequenzen des Einsatzes eingebetteter Systeme.

Ein auf diesem Buch aufbauender Kurs sollte durch eine Übung vervollständigt werden, in der beispielsweise programmierbare Roboter wie Lego Mindstorms  $^{TM}$  oder ähnliche verwendet werden. Außerdem sollten Studierende praktische Erfahrungen mit StateCharts-basierten Werkzeugen machen können.

Zusatzinformationen zu diesem Buch sind von der folgenden Webseite erhältlich:

#### $http://ls12\text{-}www.cs.tu\text{-}dortmund.de/^{\sim}marwedel/es\text{-}book$

Diese Seite beinhaltet Verweise zu Präsentationsfolien, Übungen, Hinweise zum Übungsbetrieb, Referenzen zu einer Auswahl von aktuellen Publikationen sowie Fehlerkorrekturen. Leser, die Fehler entdeckt haben oder die Vorschläge zur Verbesserung des Buches beitragen möchte, wenden sich bitte per E-Mail an Peter.Marwedel@tu-dortmund.de.

Übungen können auch anhand von Informationen aus der folgenden Auswahl von Büchern konzipiert werden: [Ganssle, 1992], [Ball, 1996], [Ball, 1998], [Barr, 1999], [Ganssle, 2000], [Wolf, 2001], [Buttazzo, 2002].

Die Verwendung von Namen in diesem Buch ohne Hinweise auf Urheberrechte oder eingetragene Warenzeichen bedeutet nicht, dass diese Namen nicht evtl. durch Dritte geschützt sind.

Viel Spaß beim Lesen dieses Buches!

Dortmund, September 2003

P. Marwedel

Herzlich willkommen zur aktualisierten Version dieses Buches! Die Verschmelzung des Kluwer- und Springer-Verlags macht es möglich, weniger als zwei Jahre nach dem Erscheinen der Erstausgabe 2003 eine neue Version dieses Buches herauszubringen. In dieser aktualisierten Version wurden alle gefundenen Tipp- und sonstigen Fehler der ersten Ausgabe korrigiert. Außerdem wurden alle Internet-Referenzen überprüft und aktualisiert. Abgesehen von diesen Änderungen ist der Inhalt des Buches gleich geblieben. Eine Liste von korrigierten Fehlern ist auf der oben genannten Webseite verfügbar.

Viel Spaß beim Lesen dieses aktualisierten Buches!

Dortmund, August 2005

P. Marwedel

Die vorliegende deutsche Fassung des Buches basiert auf der englischen Version des Buches aus dem Jahr 2005. Gegenüber dem englischen Original wurden mehrere Themen etwas ergänzt. Insbesondere wurde die Beschreibung von Scheduling-Verfahren um Beweise ergänzt, die Darstellung von Berechnungsmodellen (models of computation) überarbeitet und das Kapitel über Validierung zu einem Kapitel über Evaluation und Validierung erweitert. Dennoch sollten in der Regel die deutsche und die englische Fassung nebeneinander benutzt werden können.

Dortmund, Januar 2007

P. Marwedel (Autor des englischen Originals)

L. Wehmeyer (Übersetzer der deutschen Ausgabe)

Die vorliegende korrigierte Fassung der ersten Auflage der deutschen Ausgabe unterscheidet sich von der ursprünglichen Fassung der ersten Auflage nur durch die Beseitigung von Druckfehlern und die Überprüfung aller Referenzen auf das World Wide Web. Fehlermeldungen von Melanie Schmidt, Jan-Philipp Kappmeier und Matthias Steinkamp wurden berücksichtigt. Reinhard von Hanxleden (Universität Kiel) schlug neue Formulierungen im Abschnitt über Esterel vor. Beide Fassungen können nebeneinander benutzt werden.

Dortmund, April 2008

P. Marwedel

# Danksagung

Meine Doktoranden, besonders Lars Wehmeyer, haben eine Vorabversion des Buches gründlich Korrektur gelesen. Die Teilnehmer des Kurses "Introduction to Embedded Systems" im Sommer 2003, insbesondere Lars Bensmann, haben ebenfalls zum Buch beigetragen. Außerdem haben die folgenden Kollegen und Studierenden Kommentare und Hinweise gegeben, die in das Buch eingearbeitet wurden: W. Müller, F. Rammig (U. Paderborn), W. Rosenstiel (U. Tübingen), R. Dömer (UC Irvine) und W. Kluge (U. Kiel). Zur Vorbereitung und Zusammenstellung des Buches wurden Materialien der folgenden Personen verwendet: G. C. Buttazzo, D. Gajski, R. Gupta, J. P. Hayes, H. Kopetz, R. Leupers, R. Niemann, W. Rosenstiel und H. Takada. Korrekturen zur ersten Ausgabe dieses Buches wurden beigetragen von David Hec. Thomas Wiederkehr und Thorsten Wilmer. Eine Vorabversion der deutschen Fassung des Buches wurde von Martin Faßbach, Fatih Gedikli, Gordon Schlechter, Karl-Heinz Temme und Matthias Wiedenhorst Korrektur gelesen. Studierende des Kurses des Wintersemesters 2007/2008 haben ebenfalls zu den Korrekturen beigetragen. Selbstverständlich ist der Autor selbst verantwortlich für alle verbleibenden Fehler.

Dank gilt all denen, die die erhöhte Arbeitsbelastung des Autors während der Entstehung dieses Buches geduldig akzeptiert haben, insbesondere die dadurch oft fehlende Zeit sowohl für berufliche als auch persönliche Partner.

Schließlich sollte noch erwähnt werden, dass Kluwer Academic Publishers die Veröffentlichung dieses Buches vom ersten Konzept an unterstützt hat. Durch die Unterstützung des Verlags wurde die Arbeit an diesem Buch vorangetrieben.

Nach der Verschmelzung von Kluwer mit dem Springer-Verlag hat der Springer-Verlag großes Interesse an der Veröffentlichung einer deutschen Ausgabe gezeigt.

# Inhaltsverzeichnis

| 1 | $\mathbf{Ein}$ | leitung                                       | g                                                               | 1  |  |

|---|----------------|-----------------------------------------------|-----------------------------------------------------------------|----|--|

|   | 1.1            | Begrif                                        | fe und Abgrenzung                                               | 1  |  |

|   | 1.2            | Anwendungsgebiete                             |                                                                 |    |  |

|   | 1.3            | Wachsende Relevanz von eingebetteten Systemen |                                                                 |    |  |

|   | 1.4            | tur dieses Buches                             | 10                                                              |    |  |

| 2 | Spe            | zifikat                                       | ionssprachen                                                    | 13 |  |

|   | 2.1            | Anfor                                         | derungen                                                        | 13 |  |

|   | 2.2            | Berecl                                        | hnungsmodelle                                                   | 17 |  |

|   | 2.3            | State                                         | Charts                                                          | 18 |  |

|   |                | 2.3.1                                         | Modellierung von Hierarchie                                     | 19 |  |

|   |                | 2.3.2                                         | Zeitbedingungen                                                 | 24 |  |

|   |                | 2.3.3                                         | Kantenbeschriftungen und State<br>Mate-Semantik $\ldots \ldots$ | 25 |  |

|   |                | 2.3.4                                         | Bewertung und Erweiterungen                                     | 28 |  |

|   | 2.4            | Allger                                        | neine Spracheigenschaften                                       | 29 |  |

|   |                | 2.4.1                                         | Synchrone und asynchrone Sprachen                               | 29 |  |

|   |                | 2.4.2                                         | Prozess-Konzepte                                                | 30 |  |

|   |                | 2.4.3                                         | Synchronisation und Kommunkation                                | 30 |  |

|   |                | 2.4.4                                         | Spezifikation von Zeitbedingungen                               | 31 |  |

|   |                | 2.4.5                                         | Nicht-Standard-Ein-/Ausgabegeräte                               | 32 |  |

|   | 2.5            | SDL .                                         |                                                                 | 32 |  |

|   | 2.6            | Petrinetze                                    |                                                                 |    |  |

|   |                | 2.6.1                                         | Einführung                                                      | 39 |  |

|   |                | 2.6.2                                         | Bedingungs-/Ereignisnetze                                       | 42 |  |

|   |                | 2.6.3                                         | Stellen-/Transitionen-Netze                                     | 43 |  |

|   |                |                                               |                                                                 |    |  |

## XVI Inhaltsverzeichnis

3

|      | 2.6.4                   | Prädikat-/Ereignis-Netze                        | 47 |  |

|------|-------------------------|-------------------------------------------------|----|--|

|      | 2.6.5                   | Bewertung                                       | 49 |  |

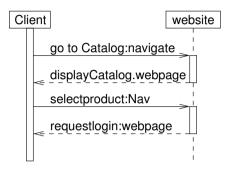

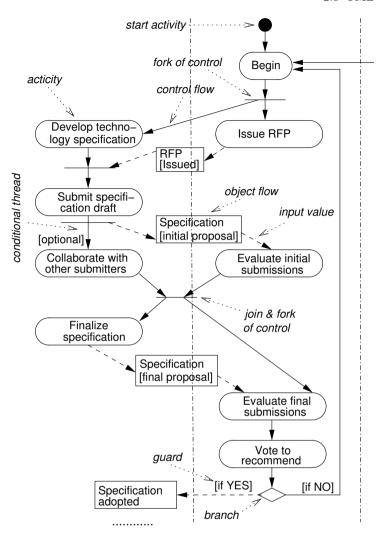

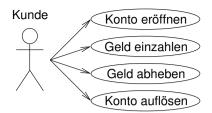

| 2.7  | Message Sequence Charts |                                                 |    |  |

| 2.8  | UML                     |                                                 | 51 |  |

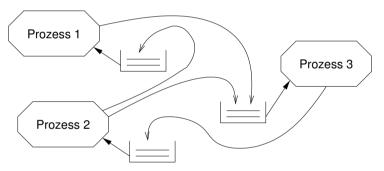

| 2.9  | Prozessnetze            |                                                 |    |  |

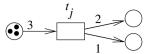

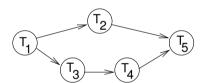

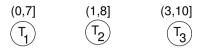

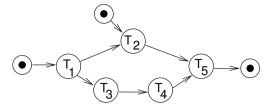

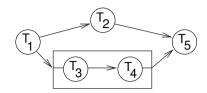

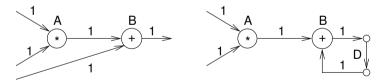

|      | 2.9.1                   | Taskgraphen                                     | 55 |  |

|      | 2.9.2                   | Asynchroner Nachrichtenaustausch                | 58 |  |

|      | 2.9.3                   | Synchroner Nachrichtenaustauch                  | 60 |  |

| 2.10 | Java .                  |                                                 | 63 |  |

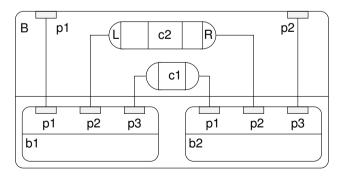

| 2.11 | VHDL                    |                                                 | 64 |  |

|      | 2.11.1                  | Einführung                                      | 64 |  |

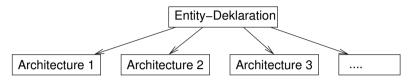

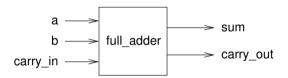

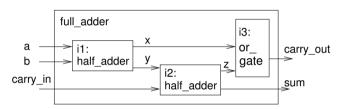

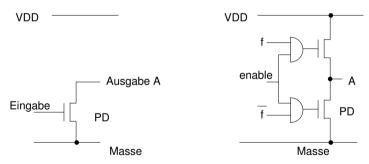

|      | 2.11.2                  | Entities und Architectures                      | 66 |  |

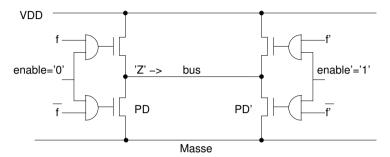

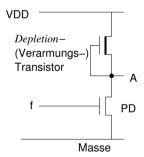

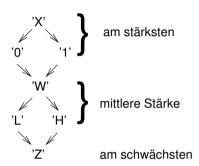

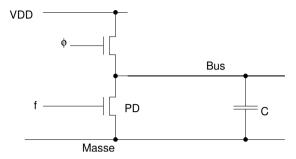

|      | 2.11.3                  | Mehrwertige Logik und IEEE 1164 $\ldots \ldots$ | 68 |  |

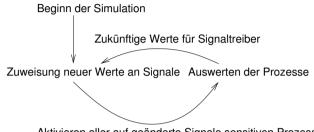

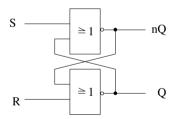

|      | 2.11.4                  | VHDL-Prozesse und Simulations-Semantik          | 75 |  |

| 2.12 | System                  | nC                                              | 80 |  |

| 2.13 | Verilog                 | g und SystemVerilog                             | 81 |  |

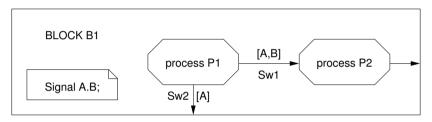

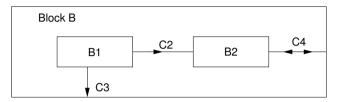

| 2.14 | SpecC                   |                                                 | 83 |  |

| 2.15 | Weiter                  | re Sprachen                                     | 84 |  |

| 2.16 | Ebene                   | n der Hardware-Modellierung                     | 87 |  |

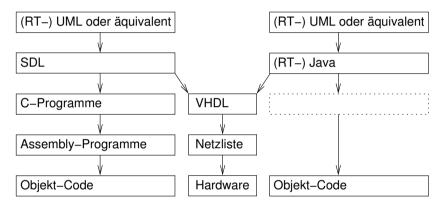

| 2.17 | Vergle                  | ich der Sprachen                                | 90 |  |

| 2.18 | Verläs                  | slichkeitsanforderungen                         | 92 |  |

| Har  | dwara                   | eingebetteter Systeme                           | 95 |  |

| 3.1  |                         | rung                                            |    |  |

| 3.2  |                         | be                                              |    |  |

| 0.2  | 3.2.1                   | Sensoren                                        |    |  |

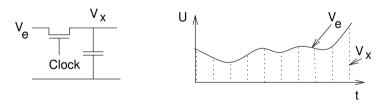

|      | 3.2.2                   | Sample-and-Hold-Schaltungen                     |    |  |

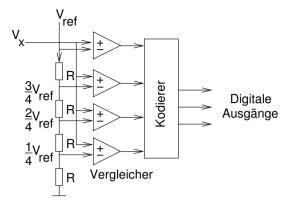

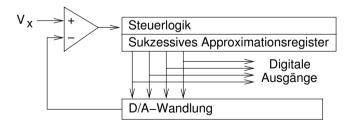

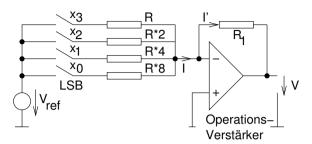

|      | 3.2.3                   | A/D-Wandler                                     |    |  |

| 3.3  |                         | nunikation                                      |    |  |

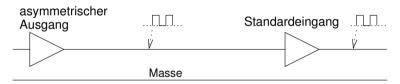

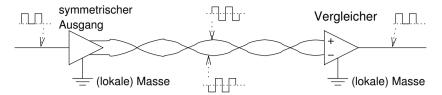

|      | 3.3.1                   | Anforderungen                                   |    |  |

|      | 3.3.2                   | Elektrische Robustheit                          |    |  |

|      | 3.3.3                   | Garantieren von Echtzeitverhalten               |    |  |

|      | 3.3.4                   | Beispiele                                       |    |  |

| 3.4  |                         | peitungseinheiten                               |    |  |

|      |                         |                                                 |    |  |

|   |     | 3.4.1  | Überblick                                                  |  |  |

|---|-----|--------|------------------------------------------------------------|--|--|

|   |     | 3.4.2  | Anwendungsspezifische integrierte Schaltkreise (ASICs) 109 |  |  |

|   |     | 3.4.3  | Prozessoren                                                |  |  |

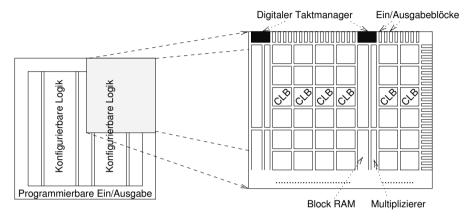

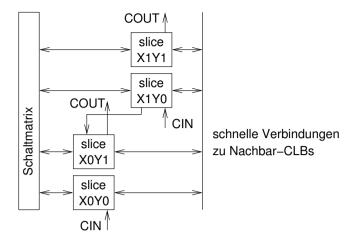

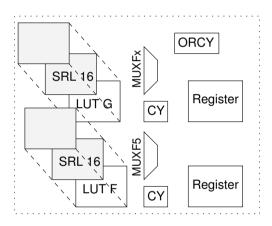

|   |     | 3.4.4  | Rekonfigurierbare Logik                                    |  |  |

|   | 3.5 | Speich | ner                                                        |  |  |

|   | 3.6 | Ausga  | ıbe131                                                     |  |  |

|   |     | 3.6.1  | D/A-Wandler                                                |  |  |

|   |     | 3.6.2  | Aktuatoren                                                 |  |  |

| 4 | Ein | gebett | sete Betriebssysteme, <i>Middleware</i> und Scheduling 135 |  |  |

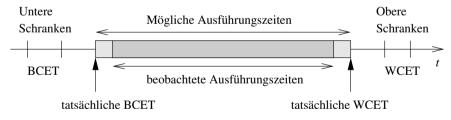

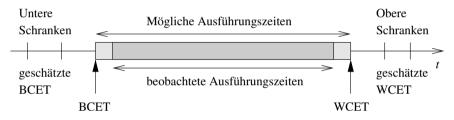

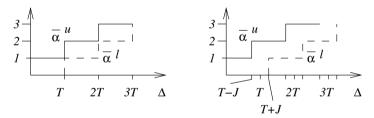

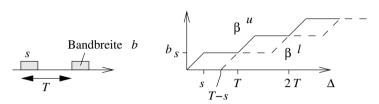

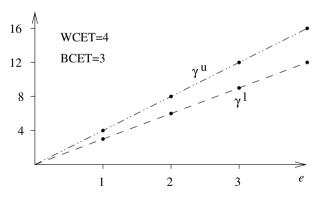

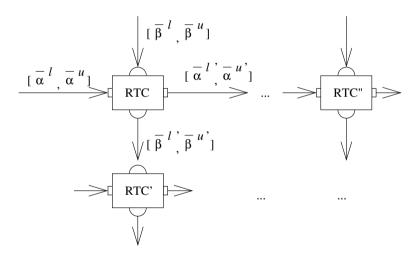

|   | 4.1 | Schra  | nken von Ausführungszeiten                                 |  |  |

|   | 4.2 | -      |                                                            |  |  |

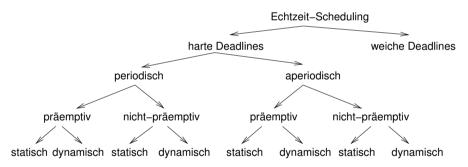

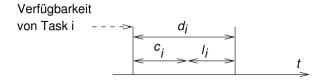

|   |     | 4.2.1  | Klassifikation von Scheduling-Algorithmen                  |  |  |

|   |     | 4.2.2  | Aperiodisches Scheduling                                   |  |  |

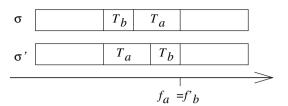

|   |     | 4.2.3  | Periodisches Scheduling                                    |  |  |

|   |     | 4.2.4  | Ressourcen-Zugriffs-Protokolle                             |  |  |

|   | 4.3 | Einge  | bettete Betriebssysteme                                    |  |  |

|   |     | 4.3.1  | Allgemeine Anforderungen                                   |  |  |

|   |     | 4.3.2  | Echtzeitbetriebssysteme                                    |  |  |

|   | 4.4 | Middl  | <i>leware</i>                                              |  |  |

|   |     | 4.4.1  | Echtzeit-Datenbanken                                       |  |  |

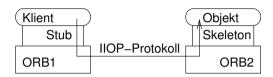

|   |     | 4.4.2  | Zugriff auf entfernte Objekte                              |  |  |

| 5 | Imp | olemen | ntierung eingebetteter Systeme:                            |  |  |

|   | Har |        | e-/Software-Codesign                                       |  |  |

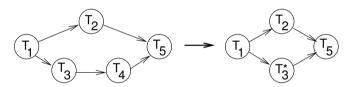

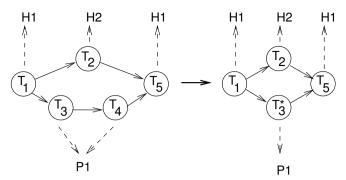

|   | 5.1 | _      | nisation der Nebenläufigkeit auf Task-Ebene                |  |  |

|   | 5.2 | High-  | Level-Optimierungen                                        |  |  |

|   |     | 5.2.1  | Umwandlung von Gleitkomma- in Festkomma-<br>Darstellung    |  |  |

|   |     | 5.2.2  | Einfache Schleifentransformationen                         |  |  |

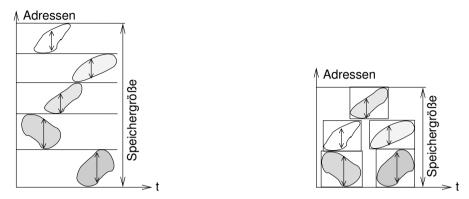

|   |     | 5.2.3  | Kachel-/Blockweise Verarbeitung von Schleifen 179          |  |  |

|   |     | 5.2.4  | Aufteilen von Schleifen                                    |  |  |

|   |     | 5.2.5  | Falten von Feldern                                         |  |  |

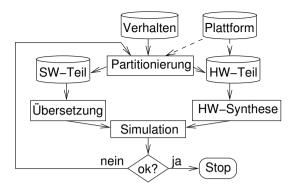

|   | 5.3 | Hardy  | ware-/Software-Partitionierung                             |  |  |

|   |     | 5.3.1  | Einleitung                                                 |  |  |

## XVIII Inhaltsverzeichnis

|     |       | 5.3.2                                | COOL                                                                          | 187 |  |

|-----|-------|--------------------------------------|-------------------------------------------------------------------------------|-----|--|

|     | 5.4   | Comp                                 | iler für eingebettete Systeme                                                 | 197 |  |

|     |       | 5.4.1                                | Einführung                                                                    | 197 |  |

|     |       | 5.4.2                                | Energieoptimierende Compiler                                                  | 198 |  |

|     |       | 5.4.3                                | Compiler für digitale Signalverarbeitung                                      | 202 |  |

|     |       | 5.4.4                                | Compiler für Multimedia-Prozessoren                                           | 205 |  |

|     |       | 5.4.5                                | Compiler für VLIW-Prozessoren                                                 | 205 |  |

|     |       | 5.4.6                                | Compiler für Netzwerkprozessoren                                              | 206 |  |

|     |       | 5.4.7                                | Compiler-Erzeugung, retargierbare Compiler und Untersuchung des Entwurfsraums | 207 |  |

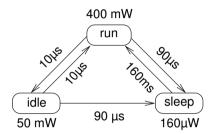

|     | 5.5   | Verson                               | gungsspannungs-Anpassung und Energie-Management                               | 207 |  |

|     |       | 5.5.1                                | Dynamische Anpassung der Versorgungsspannung                                  | 207 |  |

|     |       | 5.5.2                                | Dynamisches Power-Management                                                  | 211 |  |

| 6   | Eva   | Evaluierung und Validierung          |                                                                               |     |  |

|     | 6.1   | Einlei                               | tung                                                                          | 213 |  |

|     | 6.2   | Pareto                               | o-Optimalität                                                                 | 215 |  |

|     | 6.3   | Simulation                           |                                                                               |     |  |

|     | 6.4   | Rapid Prototyping und Emulation      |                                                                               |     |  |

|     | 6.5   | Leistungsbewertung                   |                                                                               |     |  |

|     | 6.6   | Bewertung des Energieverbrauchs      |                                                                               |     |  |

|     | 6.7   | Risiko- und Verlässlichkeits-Analyse |                                                                               |     |  |

|     | 6.8   | 8 Formale Verifikation               |                                                                               |     |  |

|     | 6.9   | Tester                               | 1                                                                             | 236 |  |

|     |       | 6.9.1                                | Betrachteter Bereich                                                          | 236 |  |

|     |       | 6.9.2                                | Testfreundlicher Entwurf                                                      | 237 |  |

|     |       | 6.9.3                                | Selbstestprogramme                                                            | 240 |  |

|     | 6.10  | Fehler                               | simulation                                                                    | 241 |  |

|     | 6.11  | Fehler                               | injektion                                                                     | 242 |  |

| Lit | eratu | ırverze                              | eichnis                                                                       | 245 |  |

| Sac | hver  | zoichn                               | ie                                                                            | 250 |  |

# Einleitung

### 1.1 Begriffe und Abgrenzung

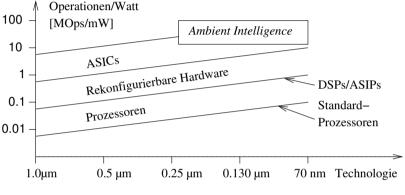

Bis in die späten 80er Jahre war die Informationsverarbeitung mit großen Mainframe-Rechnern und riesigen Bandlaufwerken verbunden. Während der 90er Jahre hat sich die Informationsverarbeitung zu den Personal Computern, den PCs, verlagert. Dieser Trend zur Miniaturisierung geht weiter, und die Mehrzahl informationsverarbeitender Geräte werden in naher Zukunft kleine, teilweise auch tragbare Computer sein, die in größere Produkte integriert sind. Das Vorhandensein von Prozessoren in diesen umgebenden Produkten, wie z.B. in Telekommunikationsgeräten, wird weniger sichtbar sein als beim klassischen PC. Daher wird dieser Trend als der verschwindende Computer bezeichnet. Allerdings bedeutet dieser Begriff nicht, dass die Computer tatsächlich verschwinden werden, sondern vielmehr, dass sie überall sein werden. Diese neue Art von Anwendungen der Informationsverarbeitung wird auch ubiquitous computing (allgegenwärtiges Rechnen), pervasive computing [Hansmann, 2001], [Burkhardt, 2001] oder ambient intelligence [Marzano und Aarts, 2003] genannt. Diese drei Begriffe beschäftigen sich mit unterschiedlichen Nuancen der zukünftigen Informationsverarbeitung. Ubiquitous Computing konzentriert sich auf die langfristige Zielsetzung, Informationen jederzeit und überall zur Verfügung zu stellen, wohingegen pervasive computing sich mehr mit praktischen Aspekten, wie etwa der Ausnutzung bereits vorhandener Technologie, beschäftigt. Im Bereich ambient intelligence findet man einen Schwerpunkt auf der Kommunikationstechnologie im Wohnbereich der Zukunft sowie im Bereich der intelligenten Gebäudetechnik. Eingebettete Systeme sind einer der Ausgangspunkte dieser drei Gebiete und sie steuern einen Großteil der notwendigen Technologie bei. Eingebettete Systeme sind informationsverarbeitende Systeme, die in ein größeres Produkt integriert sind, und die normalerweise nicht direkt vom Benutzer wahrgenommen werden. Beispiele für eingebettete Systeme sind informationsverarbeitende Systeme in Telekommunikationsgeräten, in Transportsystemen

wie Autos, Zügen, Flugzeugen, in Fabriksteuerungen und in Unterhaltungsgeräten. Diese Systeme haben die folgenden gemeinsamen Charakteristiken:

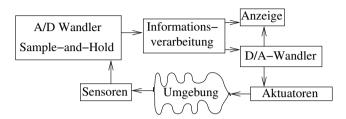

- Häufig sind eingebettete Systeme mit der physikalischen Umwelt verbunden. Sensoren sammeln Informationen über die Umgebung und Aktuatoren<sup>1</sup> nehmen Einfluss auf die Umwelt.

- Eingebettete Systeme müssen verlässlich sein.

Viele eingebettete Systeme sind sicherheitskritisch und müssen deshalb verlässlich arbeiten. Atomkraftwerke sind ein Beispiel für extrem sicherheitskritische Systeme, die zumindest zum Teil von Software gesteuert werden. Verlässlichkeit ist auch in anderen Systemen wichtig, so etwa in Autos, Zügen, Flugzeugen usw. Ein Hauptgrund, warum diese Systeme sicherheitskritisch sind, ist die Tatsache, dass sie direkt mit ihrer Umgebung in Verbindung stehen und einen unmittelbaren Einfluss auf diese Umgebung haben.

Verlässlichkeit beinhaltet die folgenden Eigenschaften eines Systems:

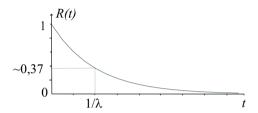

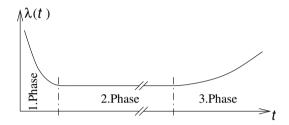

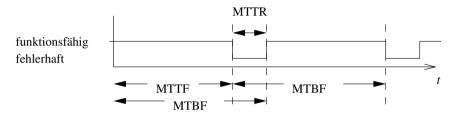

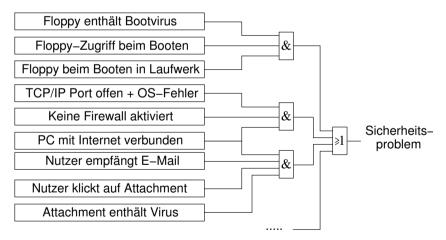

- 1. **Zuverlässigkeit:** Die Zuverlässigkeit ist die Wahrscheinlichkeit, dass ein System nicht ausfällt.

- 2. Wartbarkeit: Die Wartbarkeit ist die Wahrscheinlichkeit, dass ein ausgefallenes System innerhalb einer bestimmten Zeitspanne wieder repariert werden kann.

- 3. Verfügbarkeit: Die Verfügbarkeit ist die Wahrscheinlichkeit, dass ein System korrekt arbeitet. Sowohl Zuverlässigkeit als auch Wartbarkeit müssen hoch sein, um eine hohe Verfügbarkeit zu erreichen.

- 4. **Sicherheit:** Dieser Ausdruck beschreibt die Eigenschaft, dass ein ausfallendes System keinen Schaden verursacht.

- 5. **Integrität:** Dieser Begriff beschreibt die Eigenschaft, dass vertrauliche Daten geheim bleiben und dass die Authentizität der Kommunikation gewährleistet ist.

- Eingebettete Systeme müssen **effizient** sein. Die folgenden Größen können dazu verwendet werden, die Effizienz von eingebetteten Systemen zu beschreiben:

- 1. Energie: Viele eingebettete Systeme sind in tragbare Geräte integriert, die ihre Energie über Batterien beziehen. Nach aktuellen Vorhersagen [SEMATECH, 2003] wird die Kapazität von Batterien nur langsam wachsen. Allerdings wachsen die Anforderungen an die Rechenkapazität, insbesondere für Multimedia-Anwendungen, sehr stark an, und die Kunden erwarten trotzdem lange Batterielaufzeiten. Daher muss die verfügbare elektrische Energie sehr effizient eingesetzt werden.

$<sup>^{1}\,</sup>$  Aktuatoren sind in diesem Kontext Geräte, die numerische Werte in physikalische Größen umwandeln.

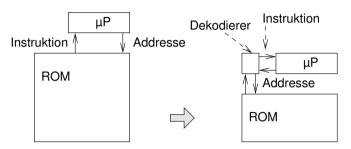

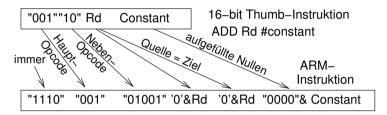

- 2. Codegröße: Der Code, der auf einem eingebetteten System ausgeführt werden soll, muss innerhalb des Systems selbst gespeichert werden. Typischerweise gibt es in solchen Systemen keine Festplatte, auf der das Programm abgelegt werden kann. Das dynamische Hinzufügen von Code ist (noch) eine Ausnahmeerscheinung und tritt nur z.B. bei Java-Telefonen oder Set-Top-Boxen auf. Aufgrund der Rahmenbedingungen muss die Größe des Codes so klein wie möglich sein, er muss aber dennoch das gewünschte Verhalten zeigen. Dies gilt insbesondere für Systems On a Chip (SOCs), bei denen sich alle informationsverarbeitenden Schaltkreise auf einem einzigen Chip befinden. Wenn der Befehlsspeicher auf diesem Chip integriert werden soll, muss er zwangsläufig sehr effizient genutzt werden.

- 3. Laufzeit-Effizienz: Die gewünschte Funktionalität eines eingebetteten Systems sollte mittels eines minimalen Aufwands an Ressourcen zur Verfügung gestellt werden. Auch Zeitbedingungen sollten unter Verwendung minimaler Hardware- und Energie-Ressourcen sicher eingehalten werden können. Außerdem ist es wichtig, dass wirklich nur notwendige Hardware-Komponenten vorhanden sind. Komponenten, die nicht in der Lage sind, die maximal benötigte Zeit zur Ausführung einer Aufgabe (die sog. Worst Case Execution Time (WCET)) zu verbessern, wie z.B. viele Caches können in zeitkritischen Systemen weggelassen werden.

- 4. **Gewicht:** Alle tragbaren Geräte müssen ein möglichst geringes Gewicht aufweisen, da dies oft einen Kaufanreiz für ein bestimmtes System darstellt.

- 5. **Preis:** Für eingebettete Systeme, die in großen Stückzahlen hergestellt werden, insbesondere solche in Konsumelektronik, ist der Wettbewerb auf dem Markt ein sehr wichtiger Aspekt. Daher müssen sowohl Hardware-Komponenten als auch das Software-Entwicklungs-Budget sorgfältig und effizient genutzt werden.

- Diese Systeme werden meistens für eine bestimmte Applikation entworfen. Beispielsweise wird ein Prozessor im Steuergerät eines Autos oder eines Zuges nur immer genau seine Steuerungs-Software ausführen. Niemand würde versuchen, auf einem solchen System ein Computerspiel oder eine Tabellenkalkulation auszuführen. Dafür gibt es zwei Hauptgründe:

- 1. Würde man die Ausführung anderer Programme auf diesen Systemen zulassen, würden sie dadurch weniger verlässlich.

- 2. Die Ausführung anderer Programme ist nur möglich, wenn entsprechende Ressourcen wie z.B. Speicher ungenutzt sind. In einem effizienten System sollten allerdings alle Ressourcen effizient genutzt werden.

- Die meisten eingebetteten Systeme haben keine Tastatur, keine Maus und keine großen Bildschirme als Benutzerschnittstelle. Stattdessen besitzen sie

#### 1 Einleitung

4

ein spezialisiertes Benutzer-Interface, das z.B. aus Knöpfen, einem Lenkrad, Pedalen usw. bestehen kann. Aus diesem Grund nimmt der Benutzer das informationsverarbeitende System im Hintergrund kaum wahr. Diese neue Computer-Ära wurde deshalb auch durch das Schlagwort des verschwindenden Computers charakterisiert.

• Viele eingebettete Systeme müssen Echtzeit-Bedingungen einhalten. Wenn die Berechnungen nicht innerhalb einer festgelegten Zeitspanne durchgeführt werden, kann dies zu schweren Qualitätseinbußen führen (wenn z.B. die Audio- oder Videoqualität durch Aussetzer oder Sprünge leidet), oder es kann sogar zu körperlichem Schaden des Benutzers führen (wenn sich z.B. Systeme in Autos, Zügen oder Flugzeugen nicht wie vorgesehen verhalten). Zeitbedingungen, deren Nichteinhalten zu einer Katastrophe führen kann, heißen harte Zeitbedingungen [Kopetz, 1997]. Alle anderen Zeitbedingungen heißen weiche Zeitbedingungen.

Viele aktuelle informationsverarbeitende Systeme verwenden Techniken, um die durchschnittliche Geschwindigkeit zu erhöhen. So verbessern etwa Caches die durchschnittliche Leistungsfähigkeit eines Systems. In anderen Fällen wird eine zuverlässige Kommunikation dadurch erreicht, dass bestimmte Nachrichten wiederholt werden. Pakete werden etwa von Internet-Protokollen erneut verschickt, wenn die Originalnachricht verlorengegangen ist. Im Durchschnitt führen solche wiederholten Sendevorgänge (hoffentlich) nur zu einer geringen Verringerung der Übertragungsgeschwindigkeit, obwohl die Verzögerung für eine bestimmte Nachricht Größenordnungen über der normalen Verzögerungszeit liegen kann. Im Bereich der echtzeitfähigen Systeme ist eine Argumentation, die auf durchschnittlicher Leistungsfähigkeit aufbaut, nicht akzeptabel. Eine garantierte System-Antwortzeit muss ohne statistische Argumente erklärt werden können [Kopetz, 1997].

- Viele eingebettete Systeme sind hybride Systeme. Das bedeutet, sie enthalten sowohl analoge als auch digitale Schaltungsteile. Analoge Teile verarbeiten kontinuierliche Signalwerte in kontinuierlicher Zeit, wohingegen digitale Teile diskrete Signalwerte in diskreten Zeitschritten verarbeiten.

- Typischerweise sind eingebettete Systeme reaktive Systeme, die man wie folgt definieren kann: Ein reaktives System ist ein System, das in kontinuierlicher Interaktion mit seiner Umgebung steht und mit einer Geschwindigkeit arbeitet, die von seiner Umwelt vorgegeben wird [Bergé et al., 1995]. Reaktive Systeme befinden sich in einem bestimmten Zustand und warten auf eine Eingabe. Nach jeder Eingabe führen sie eine Rechnung durch, erzeugen eine Ausgabe und wechseln in einen neuen Zustand. Aus diesem Grunde lassen sich solche Systeme gut als endliche Automaten modellieren. Reine mathematische Funktionen, die lediglich die von den Algorithmen gelösten Probleme beschreiben, wären keine geeigneten Modelle zur Beschreibung reaktiver Systeme.

• Eingebettete Systeme sind in der Lehre und in öffentlichen Diskussionen unterrepräsentiert. Um eingebettete Prozessoren wird kein Wirbel im Fernsehen und in Zeitschriftenartikeln gemacht... [Ryan, 1995]. Ein Problem bei der Vermittlung von Wissen über eingebettete Systeme ist die Ausstattung, die benötigt wird, um das Thema interessant und praktisch erfahrbar zu machen. Außerdem erschwert die hohe Komplexität von praktisch eingesetzten eingebetteten Systemen die Wissensvermittlung.

Wegen dieser gemeinsamen Charakteristiken eingebetteter Systeme erscheint es sinnvoll, gemeinsame Ansätze zum Entwurf solcher Systeme zu betrachten, statt sich nur auf einzelne Anwendungsgebiete und deren Lösung zu konzentrieren.

Natürlich hat nicht jedes eingebettete System alle oben genannten Eigenschaften. Wir können "eingebettete Systeme" also wie folgt definieren: Informationsverarbeitende Systeme, welche die meisten der oben aufgezählten Eigenschaften erfüllen, heißen eingebettete Systeme. Diese Definition beinhaltet eine gewisse Unschärfe. Allerdings erscheint es weder notwendig noch möglich, diese Unschärfe zu vermeiden.

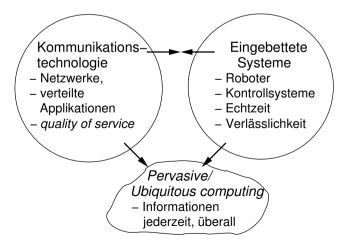

Die meisten der genannten charakteristischen Eigenschaften eingebetteter Systeme finden sich auch in den kürzlich eingeführten Gebieten des ubiquitous computing oder pervasive computing, auch bekannt als ambient intelligence. Diese Begriffe lassen sich auf deutsch mit allgegenwärtiges Rechnen übersetzen. Das Hauptziel dieser Gebiete ist es, Informationen überall und jederzeit verfügbar zu machen, weswegen sie sich auch mit Kommunikationstechnik beschäftigen. Abb. 1.1 zeigt eine graphische Darstellung, wie ubiquitous computing von eingebetteten Systemen und Kommunikationstechnik beeinflusst wird.

Abb. 1.1. Einfluss eingebetteter Systeme auf ubiquitous computing

Beispielsweise müssen beim *ubiquitous computing* Echtzeit- und Verlässlichkeitsbedingungen von eingebetteten Systemen eingehalten werden, während fundamentale Techniken der Kommunikationstechnik, wie z.B. Netzwerke, verwendet werden.

## 1.2 Anwendungsgebiete

Die folgende Liste beinhaltet Anwendungsbereiche, in denen eingebettete Systeme eingesetzt werden:

- Automobilbereich: Moderne Autos können nur noch verkauft werden, wenn sie einen beträchtliche Anteil an Elektronik enthalten, z.B. Airbag-Steuerungs-Systeme, elektronische Motorsteuerungen, ABS, Klimaanlagen, Navigationsgeräte mit GPS-Unterstützung und viele andere.

- Bordelektronik im Flugzeug: Einen Großteil des Gesamtwertes eines Flugzeugs machen heute die informationsverarbeitenden Systeme aus. Dazu gehören Flugkontrollsysteme, Anti-Kollisions-Systeme, Piloten-Informations-Systeme und andere. Die Verlässlichkeit der Systeme ist in diesem Bereich von allerhöchster Wichtigkeit.

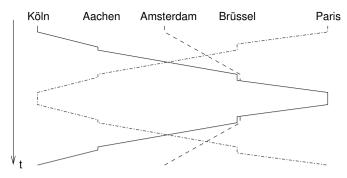

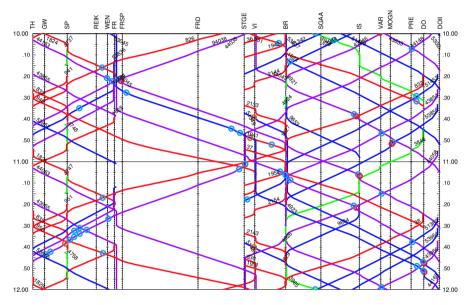

- Eisenbahntechnik: Bei Zügen, Lokomotiven und stationären Sicherheitssystemen ist die Situation ähnlich wie bei Autos und Flugzeugen. Auch hier tragen die Sicherheitssysteme einen Großteil zum gesamten Wert bei, und die Verlässlichkeit hat eine ähnlich hohe Priorität.

- Telekommunikation: Die Verkaufszahlen von Handys sind in den vergangenen Jahren so stark gestiegen wie in kaum einem anderen Bereich. Schlüsselaspekte bei der Entwicklung von Handys sind das Beherrschen der Sendetechnik, digitale Signalverarbeitung und ein geringer Energieverbrauch.

- Medizinische Systeme: Im Bereich der medizinischen Geräte gibt es durch die Verwendung von informationsverarbeitenden Geräten ein großes Innovationspotential.

- Militärische Anwendungen: Informationsverarbeitung wird seit vielen Jahren in militärischen Ausrüstungsgegenständen verwendet. Eine der ersten Computeranwendungen war die automatische Auswertung von Radarsignalen.

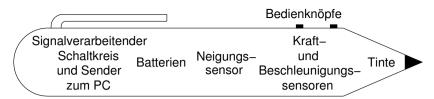

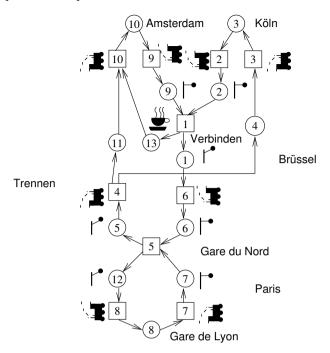

- Authentifizierungs-Systeme: Eingebettete System können zur Benutzer-Authentifizierung verwendet werden. Beispielsweise können neuartige Zahlungssysteme die Sicherheit gegenüber klassischen Systemen deutlich erhöhen. Ein Beispiel für ein solches System ist etwa der SMARTpen® [IMEC, 1997] (s. Abb. 1.2).

Abb. 1.2. SMARTpen

Der SMARTpen sieht aus wie ein Stift und analysiert während der Unterschrift physikalische Parameter wie z.B. Neigung, Anpressdruck und Beschleunigung. Diese Werte werden an einen Rechner übertragen und mit den Referenzdaten verglichen, die zu dem betreffenden Benutzer gespeichert sind. So kann man sowohl das Aussehen der Unterschrift als auch die Art und Weise, wie sie zu Papier gebracht wurde, mit der gespeicherten Information vergleichen.

Andere Authentifizierungssyteme sind etwa Fingerabdrucksensoren oder Gesichtserkennungs-Systeme.

- Unterhaltungselektronik: Video- und Audio-Geräte sind ein besonders wichtiger Sektor der Elektronikindustrie. Die Anzahl informationsverarbeitender Systeme auf diesem Gebiet erhöht sich ständig. Neue Dienste und bessere Qualität werden durch moderne Methoden der digitalen Signalverarbeitung erreicht. Viele Fernseher, Multimedia-Handys und Spielekonsolen beinhalten Hochleistungsprozessoren und -Speichersysteme. Diese stellen eine besondere Gattung eingebetteter Systeme dar.

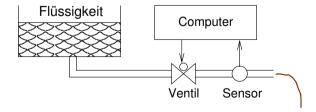

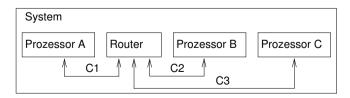

- Fabriksteuerungen: Im Bereich der Fabriksteuerungen werden eingebettete Systeme traditionell seit Jahrzehnten eingesetzt. Die Sicherheit solcher Systeme ist sehr wichtig, wohingegen der Energieverbrauch ein weniger wichtiges Kriterium ist. Das Beispiel in Abb. 1.3 (entnommen aus Kopetz [Kopetz, 1997]) zeigt einen Flüssigkeitsbehälter, der mit einem Abflussrohr verbunden ist. Das Rohr ist mit einem Ventil und einem Sensor versehen. Ein Computer kann die Daten des Sensors verwenden, um die Flüssigkeitsmenge zu steuern, die durch das Rohr abfließt.

Abb. 1.3. Regelung eines Ventils

Das Ventil ist ein Beispiel für einen Aktuator (Definition s. Seite 2).

Intelligente Gebäude: Informationsverarbeitende Systeme können verwendet werden, um den Komfort in Gebäuden zu verbessern, deren Energieverbrauch zu verringern oder um die Sicherheit zu erhöhen. Vorher unabhängige Teilsysteme müssen zu diesem Zweck miteinander verbunden werden. Der Trend geht dahin, Klimaanlagen, Lichtsteuerungen, Zugangskontrollen, Abrechnungssysteme sowie Informationsverteilung und -bereitstellung in ein einziges System zu integrieren. So kann man z.B. Energie sparen, indem man Klimaanlage, Heizung und Beleuchtung herunterfährt, wenn die betreffenden Räume leer sind. Verfügbare Räume können an geeigneten Stellen angezeigt werden, wodurch sowohl die Suche nach einem Raum für ein spontanes Meeting als auch die Aufgabe der Reinigungskräfte vereinfacht wird. Der Geräuschpegel der Klimaanlage kann an die aktuelle Situation im Raum angepasst werden. Eine intelligente Steuerung der Jalousien kann die Beleuchtung und die Nutzung der Klimaanlage optimieren. Für leere Räume können größere Temperaturschwankungen akzeptiert werden, außerdem kann die Beleuchtung entsprechend reduziert werden. Im Notfall kann eine Liste der belegten Räume am Eingang des Gebäudes angezeigt werden (vorausgesetzt, der notwendige Strom steht noch zur Verfügung).

Anfangs werden solche Systeme wohl hauptsächlich in modernen Bürogebäuden zu finden sein.

• Robotik: Im Bereich der Robotik werden eingebettete Systeme ebenfalls seit langem eingesetzt. Ein wichtiger Bereich auf diesem Gebiet ist die Mechanik. Viele der oben genannten Charakteristiken treffen auch auf die Robotik zu. Seit kurzem gibt es eine neue Art von Robotern, die Tieren oder sogar dem Menschen nachempfunden sind. Abb. 1.4 zeigt ein Beispiel.

Diese Beispiele zeigen die vielfältigen Formen und Ausprägungen eingebetteter Systeme. Warum ist es sinnvoll, all diese verschiedenen Arten von eingebetteten Systemen in einem einzigen Buch zu beschreiben? Es ist sinnvoll, weil die Informationsverarbeitung in all diesen Systemen sehr ähnlich ist, obwohl die Systeme physikalisch vollkommen unterschiedlich sind.

# 1.3 Wachsende Relevanz von eingebetteten Systemen

Die Größe des Marktes für eingebettete Systeme kann aus einer Reihe von Perspektiven analysiert werden. Wenn man z.B. die Anzahl der momentan im Betrieb befindlichen komplexen Prozessoren betrachtet, so wurde geschätzt, dass mehr als 90% dieser Prozessoren in eingebetteten Systemen verwendet werden. Viele dieser eingebetteten Prozessoren sind 8-Bit-Prozessoren, trotzdem sind 75% aller 32-Bit-Prozessoren ebenfalls in eingebettete Syste-

**Abb. 1.4.** Roboter "Johnnie" (mit freundlicher Genehmigung von H. Ulbrich, F. Pfeiffer, Lehrstuhl für Angewandte Mechanik, TU München), ©TU München

me integriert [Stiller, 2000]. Bereits 1996 wurde geschätzt, dass der durchschnittliche US-Amerikaner jeden Tag mit 60 Mikroprozessoren in Berührung kommt [Camposano und Wolf, 1996]. Einige Autos der Luxusklasse beinhalten mehr als 100 Prozessoren<sup>2</sup>. Diese Zahlen sind viel größer als man normalerweise annimmt, da vielen Menschen nicht bewusst ist, dass sie Prozessoren verwenden. Wie wichtig eingebettete Systeme sind, ist auch von der Journalistin Mary Ryan geäußert worden [Ryan, 1995]:

"... eingebettete Chips bilden das Rückgrat der von Elektronik getriebenen Welt, in der wir leben. ... sie sind in fast allem enthalten, was mit Elektrizität betrieben wird."

Vielen Vorhersagen zufolge wird der Markt für eingebettete Systeme bald viel größer sein als der Markt für PC-ähnliche Systeme. Außerdem wird die Menge an Software, die in eingebetteten Systemen verwendet wird, stark zunehmen. Nach Vaandrager wird sich "für viele Produkte im Bereich der Unterhaltungselektronik die Größe des Codes alle zwei Jahre verdoppeln "[Vaandrager, 1998].

<sup>&</sup>lt;sup>2</sup> Quelle: persönliche Kommunikation

Eingebettete Systeme bilden die Basis der sogenannten post PC era, in der sich die Informationsverarbeitung immer weiter weg von PCs, hin zu eingebetteten Systemen verlagert.

Die wachsende Zahl von Anwendungen macht es notwendig, Methoden zu entwickeln, die den Entwurf eingebetteter Systeme unterstützen. Die momentan verwendeten Technologien und Programme weisen noch starke Einschränkungen auf. So besteht ein großer Bedarf an besseren Spezifikationssprachen, an Programmen, die aus einer Spezifikation eine Implementierung ableiten, an Programmen, welche die Einhaltung von Zeitbedingungen prüfen können, an Echtzeitbetriebssystemen, an Entwurfsmethoden für energiesparende Systeme sowie an Entwurfsmethoden für verlässliche Systeme. Dieses Buch soll Grundlagen zu den wichtigsten Themen vermitteln und ein Ausgangspunkt für weitere Forschungsarbeiten auf diesem Gebiet sein.

#### 1.4 Struktur dieses Buches

Viele der vorhandenen Bücher über eingebettete Systeme erläutern und beschreiben den Einsatz von Mikrocontrollern, sowie die in Mikrocontrollern verwendeten Speicher, die Ein- und Ausgabeeinheiten sowie die Struktur der Interrupts. Es gibt zahlreiche solcher Bücher, etwa [Ganssle, 1992], [Ball, 1996], [Ball, 1998], [Barr, 1999] und [Ganssle, 2000].

Aufgrund der steigenden Komplexität eingebetteter Systeme muss dieser Blickwinkel erweitert werden und zumindest verschiedene Spezifikationssprachen, Hardware-/Software-Codesign, Compiler-Techniken, Scheduling (Ablaufplanung) sowie Validierungstechniken enthalten. Diese Gebiete werden im vorliegenden Buch behandelt. Das Ziel dieses Buches ist es, Studierenden eine Einführung in das Gebiet der eingebetteten Systeme zu geben und ihnen damit die Möglichkeit zu eröffnen, die verschiedenen Teilgebiete einzuordnen.

Als weiterführende Literatur empfehlen wir folgende Quellen (die teilweise auch während der Vorbereitung dieses Buches herangezogen wurden):

- Es gibt eine Vielzahl von Informationsquellen zu Spezifikationssprachen. Zu nennen sind frühe Bücher von Young [Young, 1982], Burns und Wellings [Burns und Wellings, 1990] sowie von Bergé [Bergé et al., 1995]. Über neuere Sprachen wie beispielsweise Java, SystemC [Müller et al., 2003], SpecC [Gajski et al., 2000] usw. gibt es sehr viele Bücher.

- Einige Ansätze zum Entwurf und zum Einsatz von Echtzeitbetriebssystemen (*Real-Time Operating Systems* (RTOS)) werden im Buch von Kopetz [Kopetz, 1997] vorgestellt.

- Echtzeit-Scheduling (Ablaufplanung) wird umfassend in den Büchern von Buttazzo [Buttazzo, 2002] und Krishna und Shin [Krishna und Shin, 1997] abgehandelt.

- Die Vorlesungsskripte von Rajiv Gupta [Gupta, 2002] geben einen Überblick über eingebettete Systeme.

- Das Gebiet der Robotik ist eng mit den eingebetteten Systemen verwandt.

Wir empfehlen für Informationen auf diesem Gebiet die Bücher von Fu,

Gonzalez und Lee [Fu et al., 1987].

- Weitere Informationen findet man in einem Buch von Vahid [Vahid, 2002], in der ARTIST Roadmap [Bouyssounouse und Sifakis, 2005] sowie im forschungsorientierten Embedded Systems Handbook [Zurawski, 2006].

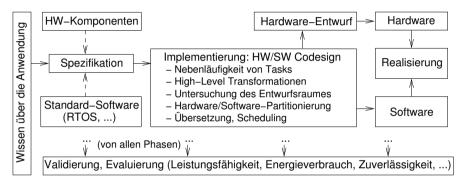

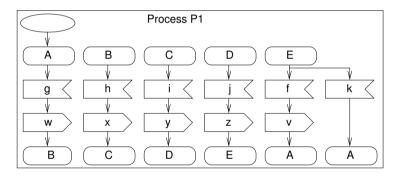

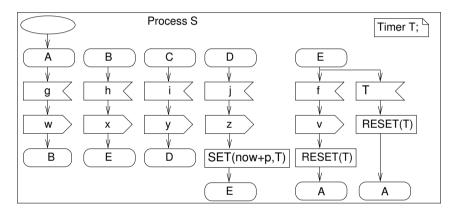

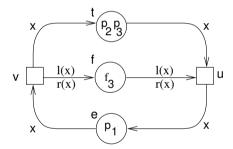

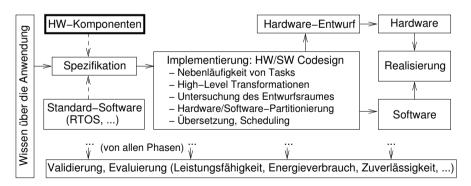

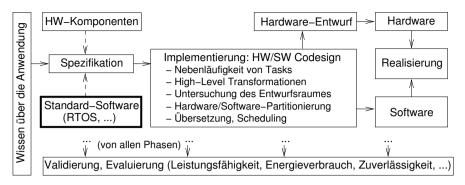

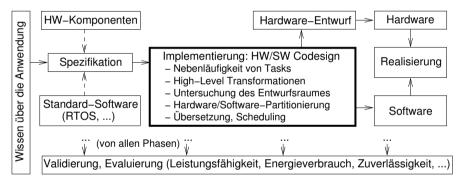

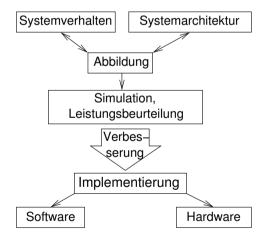

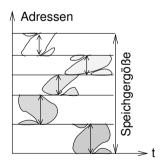

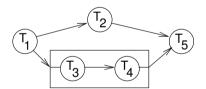

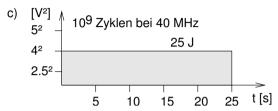

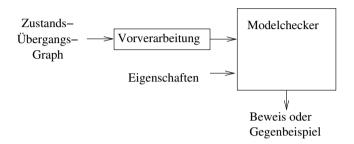

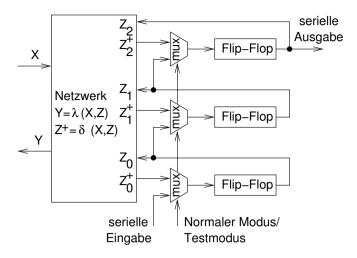

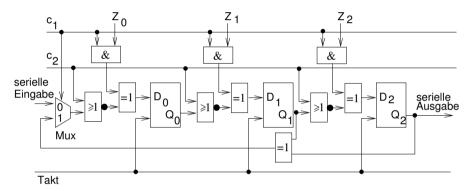

Die Struktur dieses Buches entspricht dem vereinfachten Informationsfluss beim Entwurf eingebetteter Systeme, wie er in Abb. 1.5 abgebildet ist.

Abb. 1.5. Vereinfachter Informationsfluss beim Entwurf eingebetteter Systeme

Der Informationsfluss beginnt mit einer Idee. Diese Idee muss in einer Entwurfsspezifikation beschrieben werden. Hierbei sollten zur Verfügung stehende Hard- und Software-Komponenten wiederverwendet werden.

Der eigentliche Entwurf beginnt bei der Spezifikation. Typischerweise müssen beim Entwurf eingebetteter Systeme sowohl Hardware- als auch Software-Komponenten in Betracht gezogen werden. Die Entwurfsaktivitäten beinhalten das Abbilden von durchzuführenden Operationen auf nebenläufige Tasks, High-Level-Transformationen (etwa komplexe Schleifentransformationen), das Abbilden von Aufgaben auf entweder Hardware oder Software (die sogenannte Hardware/Software-Partitionierung), Untersuchen und Evaluieren des Entwurfsraumes, Software-Übersetzung mit Hilfe von Compilern, sowie Scheduling (Ablaufplanung). Eventuell ist es notwendig, spezialisierte Hardware oder optimierte Prozessorarchitekturen zu verwenden. Der Entwurf dedizierter Hardware wird in diesem Buch allerdings nicht behandelt. Zur Übersetzung der Software in die Maschinensprache können Standard-Compiler verwendet werden. Allerdings bieten diese häufig keine spezielle Unterstützung für eingebettete Systeme. Daher werden wir auch kurz auf Compiler-Techniken eingehen, mit denen die gewünschte Effizienz der generierten Software er-

reicht werden kann. Sobald der Maschinen-Code für jede Teilaufgabe generiert wurde, kann das Scheduling präzise durchgeführt werden. Schließlich werden Software- und Hardware-Beschreibungen zu einer kompletten Beschreibung des Systems zusammengefügt. Anhand dieser Beschreibung kann dann die Produktion des Systems erfolgen.

Nach momentanem Stand der Technik kann man für keinen dieser Schritte garantieren, dass er immer korrekte Ergebnisse liefert. Daher ist es notwendig, den Entwurf zu validieren. Die Validierung besteht darin, die Beschreibung von Zwischenschritten oder des endgültigen Designs mit den anderen Beschreibungen zu vergleichen und auf Abweichungen zu überprüfen. Außerdem muss zu verschiedenen Zeitpunkten der Entwurf evaluiert werden, z.B. in Bezug auf seine Leistungsfähigkeit, seine Verlässlichkeit, Energieverbrauch, Herstellbarkeit usw.

Zu beachten ist, dass Abb. 1.5 den Fluss von Informationen über das Entwurfsobjekt darstellt. Die Abfolge von Entwurfsaktivitäten muss zu diesem Fluss konsistent sein. Das bedeutet allerdings nicht, dass die Entwurfsaktivitäten einem einfachen Pfad von der Idee hin zum fertigen Produkt entsprechen. In der Praxis müssen einige Aktivitäten wiederholt werden. So kann es notwendig sein, zu einem späteren Zeitpunkt auf die Ebene der Spezifikation zurückzugehen, um zusätzliche Informationen über die Anwendung zu erhalten. Es kann auch vorkommen, dass andere Echtzeit-Betriebssysteme in Betracht gezogen werden müssen, da das ursprünglich vorgesehene Betriebssystem die Anforderungen nicht erfüllt.

Die Kapitel dieses Buches sind analog zum Informationsfluss strukturiert: in Kapitel 2 werden Spezifikationssprachen behandelt. Wichtige Hardware-Komponenten eingebetteter Systeme werden in Kapitel 3 betrachtet. Kapitel 4 widmet sich der Beschreibung von Echtzeit-Betriebssystemen und sogenannter *Middleware* sowie Scheduling-Techniken. Standard-Entwurfstechniken zur Implementierung eingebetteter Systeme, u.a. Compiler-Techniken, werden in Kapitel 5 behandelt. Das letzte Kapitel schließlich befasst sich mit der Evaluation und Validierung.

# Spezifikationssprachen

# 2.1 Anforderungen

Gemäß dem vereinfachten Informationsfluss-Diagramm (s. Abb. 1.5) beschreibt dieses Kapitel die Anforderungen an Ansätze zur Spezifikation eingebetteter Systeme.

Es mag immer noch Fälle geben, in denen die Spezifikation eines eingebetteten Systems in einer natürlichen Sprache, wie z.B. Englisch, festgehalten wird. Dieser Ansatz ist aber vollkommen ungeeignet, denn ihm fehlen wichtige Anforderungen an Spezifikationssprachen: es muss möglich sein, eine Spezifikation auf Vollständigkeit sowie auf Widerspruchsfreiheit zu prüfen, außerdem möchte man aus der Spezifikation mit einer systematischen Vorgehensweise eine Implementierung des Systems herleiten können. Deshalb sollte die Spezifikation in Form einer maschinenlesbaren, formalen Sprache erfolgen. Spezifikationssprachen für eingebettete Systeme sollten in der Lage sein, die folgenden Sachverhalte darzustellen<sup>1</sup>:

• Hierarchie: Der Mensch ist im Allgemeinen nicht in der Lage, Systeme zu verstehen, die viele Objekte (wie z.B. Zustände, Komponenten) enthalten, die in komplexem Zusammenhang miteinander stehen. Um ein reales System zu beschreiben, benötigt man mehr Objekte als ein Mensch erfassen kann. Die Einführung von Hierarchie-Ebenen ist der einzige Weg, dieses Problem zu lösen. Hierarchie kann so eingesetzt werden, dass ein Mensch immer nur eine kleine Anzahl von Objekten auf einmal überschauen muss.

Es gibt zwei Arten von Hierarchien:

Verhaltens-Hierarchien: Verhaltenshierarchien enthalten Objekte, die notwendig sind, um das Verhalten des Gesamtsystems zu beschrei-

<sup>&</sup>lt;sup>1</sup> Zur Erstellung dieser Liste wurden Informationen aus den Büchern von Burns et al. [Burns und Wellings, 1990], Bergé et al. [Bergé et al., 1995] und Gajski et al. [Gajski et al., 1994] verwendet.

ben. Hierarchische Zustände und verschachtelte Prozeduren sind Beispiele solcher Hierarchien.

Strukturelle Hierarchien: Strukturelle Hierarchien beschreiben, wie das Gesamtsystem aus einzelnen physikalischen Komponenten zusammengesetzt ist.

Eingebettete Systeme können z.B. aus Prozessoren, Speichern, Aktuatoren und Sensoren bestehen. Prozessoren wiederum enthalten Register, Multiplexer und Addierwerke. Multiplexer bestehen aus Gattern.

- Zeitverhalten: Da das Einhalten von Zeitbedingungen eine grundlegende Anforderung an eingebettete Systeme ist, muss es möglich sein, diese Zeitbedingungen explizit in der Spezifikation zu erfassen.

- Zustandsorientiertes Verhalten: Es wurde bereits in Kapitel 1 erwähnt, dass Automaten eine gute Darstellungsmöglichkeit für reaktive Systeme sind. Aus diesem Grund sollte es einfach sein, zustandsorientiertes Verhalten, wie es endliche Automaten zeigen, zu beschreiben. Klassische Automatenmodelle sind allerdings nicht ausreichend, da sie weder Zeitbedingungen noch Hierarchie unterstützen.

- Ereignisbehandlung: Da eingebettete Systeme oft reaktive Systeme sind, müssen Mechanismen zur Beschreibung von Ereignissen existieren. Solche Ereignisse können externe (von der Umwelt erzeugte) oder interne (von Komponenten des Systems erzeugte) Ereignisse sein.

- Keine Hindernisse bei der Erzeugung von effizienten Implementierungen: Da eingebettete Systeme effizient sein müssen, sollte die Spezifikationssprache eine effiziente Realisierung des Systems nicht behindern oder unmöglich machen.

- Beispiel: Angenommen, eine Spezifikationstechnik setze die Existenz einer virtuellen Maschine oder eines umfangreichen Simulators voraus. Dann müssen diese selbst bei kleinen Spezifikationen implementiert werden, was den Entwurf insgesamt nicht mehr effizient werden lassen kann.

- Unterstützung für den Entwurf verlässlicher Systeme: Spezifikationstechniken sollten den Entwurf von verlässlichen Systemen unterstützen. Beispielsweise sollte die Spezifikationssprache eine eindeutige Semantik haben und den Einsatz formaler Verifikationstechniken erlauben. Außerdem sollte es möglich sein, Sicherheits- und Authentizitäts-Anforderungen zu beschreiben.

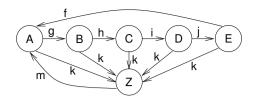

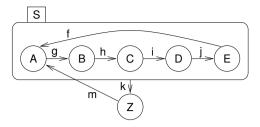

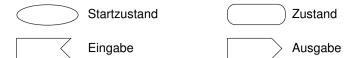

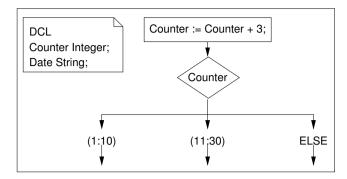

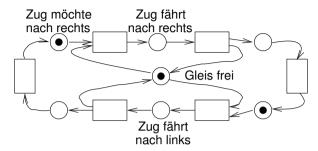

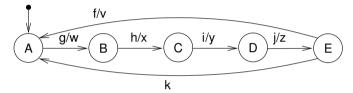

- Ausnahmeorientiertes Verhalten: In vielen praktischen Systemen treten Ausnahmen auf. Um verlässliche Systeme entwerfen zu können, muss die Behandlung solcher Ausnahmesituationen einfach zu beschreiben sein. Es ist nicht ausreichend, wenn man die Ausnahmebehandlung z.B. für jeden einzelnen Zustand angeben muss, wie das etwa bei klassischen Automatenmodellen der Fall ist. Beispiel: In Abb. 2.1 soll die Eingabe k das Auftreten einer Ausnahme darstellen.

Abb. 2.1. Zustandsdiagramm mit Ausnahme k

Die Angabe einer solchen Ausnahme für jeden Zustand macht das Zustandsdiagramm sehr komplex und unübersichtlich, besonders bei großen Diagrammen mit vielen Transitionen. Wir werden später zeigen, wie man all diese Ausnahme-Transitionen durch eine einzige Transition ersetzen kann.

- Nebenläufigkeit: Viele praktisch relevante Systeme sind verteilte, nebenläufige Systeme. Aus diesem Grunde muss Nebenläufigkeit oder Parallelität einfach zu spezifizieren sein.

- Synchronisation und Kommunikation: Zeitgleich ablaufende Aktivitäten innerhalb eines Systems müssen miteinander kommunizieren und sich über die Verwendung von Ressourcen absprechen können. So ist es zum Beispiel häufig notwendig, gegenseitigen Ausschluss zu realisieren.

- Programmiersprachenelemente: Gewöhnliche Programmiersprachen haben sich als gängige Methode zur Beschreibung von Berechnungsvorschriften etabliert. Daher sollten Elemente von Programmiersprachen in der Spezifikation verwendet werden können. Klassische Zustandsdiagramme erfüllen diese Anforderung nicht.

- Ausführbarkeit: Eine Spezifikation ist nicht automatisch äquivalent zur ursprünglichen Idee des Designers. Das Ausführen der Spezifikation stellt eine Möglichkeit der Plausibilitätsprüfung für den Entwurf dar. Spezifikationen, die Programmiersprachenelemente verwenden, sind in diesem Kontext von Vorteil.

- Unterstützung für den Entwurf großer Systeme: Der Trend geht hin zu immer größeren und komplexeren Programmen, die auf eingebetteten Systemen ablaufen. In der Software-Technologie gibt es Mechanismen, um solche großen Systeme handhabbar zu machen, z.B. die Objektorientierung. Solche Mechanismen sollten auch in der Spezifikationsmethode Einsatz finden.

- Unterstützung von spezifischen Anwendungsbereichen: Es wäre natürlich schön, wenn man ein und dieselbe Spezifikationstechnik für alle möglichen eingebetteten Systeme verwenden könnte, da dies den Aufwand für die Entwicklung von Techniken minimieren würde. Allerdings ist die mögliche Bandbreite von Anwendungsgebieten so groß, dass man kaum hoffen kann, dass eine einzige Sprache alle Belange aller Anwen-

dungsbereiche gleichermaßen gut abdecken kann. Beispielsweise können kontrollflussdominierte, datenflussdominierte, zentralisierte oder verteilte Anwendungsgebiete von spezifischer *Tool*-Unterstützung für den jeweiligen Bereich profitieren.

- Lesbarkeit: Selbstverständlich muss eine Spezifikation von Menschen gelesen werden können. Nach Möglichkeit sollte sie auch maschinenlesbar sein, damit sie von einem Rechner verarbeitet werden kann.

- Portierbarkeit und Flexibilität: Spezifikationen sollten unabhängig von der für die Implementierung verwendeten spezifischen Hardware-Plattform sein, so dass man sie leicht für eine Auswahl von Zielplattformen einsetzen kann. Sie sollten so flexibel sein, dass eine kleine Änderung am Design auch nur eine kleine Änderung in der Spezifikation erfordert.

- Terminierung: Es sollte möglich sein, anhand der Spezifikation Prozesse zu identifizieren, die terminieren. Auf diese Weise wird erreicht, dass Prozessen, die keine Aufgaben mehr erfüllen, auch ihre Ressourcen entzogen werden können und dass man sich bei der Validierung mit diesen Prozessen nicht mehr beschäftigen muss.

- Unterstützung für Nicht-Standard-Ein-/Ausgabe-Geräte: Viele eingebettete Systeme verwenden andere Ein- und Ausgabegeräte als die vom PC her bekannten Tastaturen und Mäuse. Es sollte möglich sein, die Eigenschaften solcher Geräte in einfacher Weise zu spezifizieren.

- Nicht-funktionale Eigenschaften: Reale Systeme besitzen eine Reihe nicht-funktionaler Eigenschaften, wie etwa Ausfallsicherheit, Größe, Erweiterbarkeit, Lebenserwartung, Energieverbrauch, Gewicht, Recycling-Fähigkeit, Benutzerfreundlichkeit, elektromagnetische Verträglichkeit und so weiter. Es gibt keine Hoffnung, dass man all diese Eigenschaften in irgendeiner Weise formal definieren könnte.

- Angemessenes Berechnungsmodell: Zur Beschreibung von Berechnungen benötigt man ein Berechnungsmodell. Solche Modelle werden im nächsten Abschnitt behandelt.

An dieser Liste von Anforderungen kann man erkennen, dass es wohl nie eine einzige formale Sprache geben wird, die alle diese Anforderungen erfüllt. In der Praxis muss man daher in der Regel mit Kompromissen leben. Die Auswahl der Spezifikationssprache, die für ein bestimmtes Projekt verwendet wird, hängt hauptsächlich vom Anwendungsbereich und von der Umgebung, in der das System entwickelt werden soll, ab. Wir stellen im Folgenden einige Sprachen vor, die für den Entwurf eines praxisnahen Systems in Frage kommen.

## 2.2 Berechnungsmodelle

Die Anwendungen der Informationstechnologie waren bislang sehr stark an das Von-Neumann-Paradigma des sequentiellen Rechnens angelehnt. Dieses Paradigma ist für eingebettete Systeme, insbesondere für Realzeitsysteme, ungeeignet, da es beim Von-Neumann-Modell keine Möglichkeit gibt, Zeit auszudrücken. Andere Berechnungsmodelle sind für diesen Bereich eher geeignet.

Berechnungsmodelle definieren (in Anlehnung an [Lee, 1999]):

- Komponenten und die Organisation des Ablaufs von Berechnungen in diesen Komponenten: Prozeduren, Prozesse, Funktionen, endliche Automaten sind mögliche Komponenten.

- Kommunikations-Protokolle: Diese Protokolle beschreiben die Kommunikationsmöglichkeiten zwischen den Komponenten. Asynchroner Nachrichtenaustausch und Rendez-Vous-basierte Kommunikation sind Beispiele für solche Protokolle.

Beispiele für Berechnungsmodelle (siehe Lee [Lee, 1999], Janka [Janka, 2002] und Jantsch [Jantsch, 2003], die auch Nebenläufigkeit ausdrücken, können nach dem Modell der Kommunikation und dem Modell der Berechnungen in den Komponenten klassifiziert werden:

#### • Modelle der Kommunikation von Komponenten:

- Gemeinsamer Speicher (shared memory)

Bei diesem Modell greifen kommunizierende Komponenten auf gemeinsamen Speicher zu. Eine akzeptable Geschwindigkeit ergibt sich dabei nur für Komponenten, die sich in räumlicher Nähe zum Speicher befinden. Für verteilte Systeme ist dieses Modell also nicht geeignet.

Nachrichtenaustausch (message passing)

Beim Nachrichtenaustausch kommunizieren Prozesse durch das Versenden von Nachrichten miteinander. Der Versand erfolgt über **Kanäle**. Wir unterscheiden zwischen asynchronem Nachrichtenaustausch und synchronem Nachrichtenaustausch.

Beim asynchronen Nachrichtenaustausch muss der Absender nicht warten, bis der Empfänger bereit ist, die Nachricht zu empfangen. Er kann vielmehr in seinen Berechnungen fortfahren. Im Alltag entspricht das etwa dem Abschicken eines Briefes. In diesem Fall erfolgt der Versand über Kanäle, die in der Lage sind, Nachrichten zu puffern. Die meist notwendige Zwischenspeicherung von Nachrichten ist problematisch, da es zu Überläufen der Nachrichtenpuffer kommen kann.

Bei **synchronem Nachrichtenaustausch** müssen Sender und Empfänger aufeinander warten (man spricht deshalb auch von der *rendez-*

vous-Technik). Kanäle müssen hierbei nicht puffern. Dafür ergibt sich dann allerdings häufig eine Leistungseinbuße in den Komponenten.

#### • Modelle der Berechnungen in den Komponenten

#### - Von Neumann-Modell

Als Modell der Berechnung in den Komponenten können wir z.B. das von-Neumann-Modell einer sequentiellen Abarbeitung eines Befehlsstroms benutzen. Hierbei wird die Existenz von abzuarbeitenden Maschinenbefehlen vorausgesetzt.

#### - Diskretes Ereignismodell

In diesem Modell tragen alle Ereignisse einen total geordneten Zeitstempel, der die Zeit angibt, zu der das Ereignis stattfindet. Simulatoren für diskrete Ereignismodelle verfügen über eine nach der Zeit sortierte globale Ereignis-Warteschlange. Beispiele sind u.a. VHDL (s. Seite 64) und Verilog (s. Seite 81).

#### - Endliche Automaten

Klassische endliche Automaten bilden ein weiteres Modell der Berechnung in Komponenten. Ihr Verhalten wird durch die üblichen Übergangs- und Ausgabefunktionen beschrieben.

#### • Kombinierte Modelle

Manche Modelle verbinden ein bestimmtes Modell der Berechnung in den Komponenten mit einem Modell der Kommunikation. So kombiniert SDL (s. Seite 32) beispielsweise das Modell eines endlichen Automaten für die Berechnung in den Komponenten mit dem Modell des asynchronen Nachrichtenaustauschs für die Kommunikation. StateCharts dagegen kombiniert das Modell des endlichen Automaten für die einzelne Komponente mit dem Modell des gemeinsamen Speichers für die Kommunikation. CSP (s. Seite 60) und ADA (s. Seite 61) kombinieren das Modell der von-Neumann-Befehlsausführung mit dem synchronen Nachrichtenaustausch.

Verschiedene Anwendungen können die Verwendung unterschiedlicher Modelle notwendig machen. Während einige der verfügbaren Spezifikationssprachen nur eines der Modelle implementieren, erlauben andere eine Mischung verschiedener Modelle. Für die Mehrzahl der Modelle werden nachfolgend exemplarisch Beispielsprachen vorgestellt.

#### 2.3 StateCharts

Die erste praktisch eingesetzte Sprache, die hier vorgestellt werden soll, ist StateCharts. StateCharts wurde 1987 von David Harel [Harel, 1987] vorgestellt und später detaillierter beschrieben [Drusinsky und Harel, 1989]. StateCharts beschreibt kommunizierende endliche Automaten, basierend auf dem

shared memory Kommunikations-Konzept. Den Namen hat Harel angeblich so gewählt, weil es "die einzige unbenutzte Kombination von 'flow' oder 'state' mit 'diagram' oder 'chart' " war.

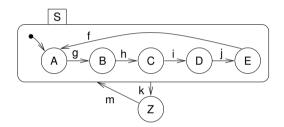

Im Abschnitt 2.1 wurde erwähnt, dass es oft notwendig ist, zustandsorientiertes Verhalten zu modellieren. Zustandsdiagramme sind dafür die klassische Methode. Abb. 2.2 (identisch mit Abb. 2.1) zeigt ein Beispiel für ein klassisches Zustandsdiagramm, das einen **endlichen Automaten** darstellt.

Abb. 2.2. Zustandsdiagramm

Kreise bezeichnen Zustände. **Deterministische** endliche Automaten, die wir hier betrachten wollen, können sich immer nur in einem ihrer Zustände befinden. Kanten stellen die Transitionen oder Übergänge zwischen den Zuständen dar. Die Kantenbeschriftung bezeichnet Ereignisse. Wenn eine Eingabe stattfindet, ändert der endliche Automat seinen Zustand der jeweiligen Kante entsprechend. Endliche Automaten können auch eine Ausgabe erzeugen (dies ist in Abb. 2.2 nicht gezeigt). Nähere Informationen zu klassischen endlichen Automaten findet man z.B. in [Kohavi, 1987].

#### 2.3.1 Modellierung von Hierarchie

StateCharts beschreiben erweiterte endliche Automaten und sind daher gut geeignet, zustandsorientiertes Verhalten abzubilden. Die wichtigste Erweiterung gegenüber klassischen Automaten ist das Konzept der **Hierarchie**. Hierarchie wird mit Hilfe von **Superzuständen** (*superstates*) eingeführt.

#### **Definitionen:**

- Zustände, die andere Zustände enthalten, heißen Superzustände

- Zustände, die in anderen Zuständen enthalten sind, heißen Unterzustände der Superzustände

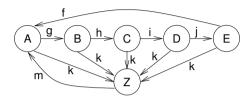

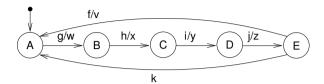

Abb. 2.3 zeigt ein StateCharts-Beispiel. Es ist eine hierarchische Version von Abb. 2.2.

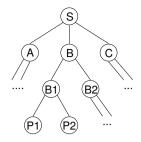

Superzustand S beinhaltet die Zustände A, B, C, D und E. Angenommen, der Automat befindet sich in Zustand Z (wir bezeichnen Z in diesem Fall auch als **aktiven Zustand**). Wenn dann die Eingabe m am Automaten erfolgt, ist A

Abb. 2.3. Hierarchisches Zustandsdiagramm

der nächste Zustand. Wenn sich der Automat in Zustand S befindet und es gibt die Eingabe k, so ist Z der nächste Zustand, unabhängig davon, in welchem der Unterzustände A, B, C, D oder E sich der Automat tatsächlich befindet. In diesem Beispiel sind alle in S enthaltenen Zustände nicht-hierarchische Zustände. Im Allgemeinen könnten die Unterzustände von S selbst wieder Superzustände sein, die weitere Unterzustände enthalten.

#### Definitionen:

- Jeder Zustand, der nicht aus anderen Zuständen besteht, heißt Basiszustand.

- Ist t ein Unterzustand von s, so heißt s Oberzustand von t.

Der endliche Automat in Abb. 2.3 kann sich zu einem bestimmten Zeitpunkt nur in genau einem der Unterzustände des Superzustands S befinden. Solche Superzustände heißen **ODER-Superzustände**. Gemeint ist hier immer ein sich gegenseitig ausschließendes ODER, da sich der Automat nur in **einem** der Zustände A, B, C, D oder E befinden kann.

**Definition:** Superzustände S heißen **ODER-Superzustände**, wenn das System, das S enthält, sich zu jedem Zeitpunkt lediglich in einem einzigen Unterzustand von S befinden kann, solange es sich in S befindet.

In Abb. 2.3 könnte die Eingabe k einer Ausnahme entsprechen, wegen der Zustand S verlassen werden muss. Das Beispiel zeigt bereits, wie man solche Ausnahmebehandlungen durch Verwendung von Hierarchie kompakt darstellen kann.

StateCharts erlaubt es, Systeme hierarchisch zu beschreiben, indem eine Beschreibung des Systems Untersysteme enthält, die wiederum Beschreibungen von Unterzuständen enthalten können und so weiter. Das Gesamtsystem kann somit in Form eines **Baumes** dargestellt werden. Die **Wurzel** dieses Baumes entspricht dem gesamten System, und die inneren Knoten entsprechen hierarchischen Beschreibungen (die im Falle von StateCharts Superzustände heißen). Die **Blätter** der Hierarchie sind nicht-hierarchische Beschreibungen (die im Falle von StateCharts Basiszustände heißen).

Bisher haben wir explizite, direkte Kanten verwendet, die zu Basiszuständen führen, um den neuen Zustand zu bestimmen. Der Nachteil dieser Art der Modellierung liegt in der Tatsache, dass man die internen Strukturen der Superzustände nicht vor der Umgebung verstecken kann. In einem echten hierarchischen Modell sollte es möglich sein, die interne Struktur zu verstecken, so dass diese später beschrieben oder sogar geändert werden kann, ohne eine Auswirkung auf die Umgebung zu haben. Dies wird durch zusätzliche Mechanismen ermöglicht, die den neuen Zustand bestimmen.

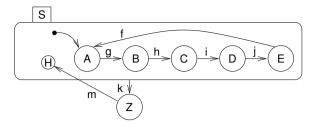

Der erste zusätzliche Mechanismus ist der **Standardzustand** (default state). Er kann in Superzuständen verwendet werden, um anzuzeigen, welche der Unterzustände betreten werden, wenn der Superzustand betreten wird. In den Diagrammen wird der Standardzustand mit Hilfe einer Kante bezeichnet, die von einem kleinen ausgefüllten Kreis zum jeweiligen Zustand geht. Abb. 2.4 zeigt ein Zustandsdiagramm, das den Standardzustands-Mechanismus verwendet. Es ist äquivalent zum Diagramm in Abb. 2.3. Man beachte, dass der kleine ausgefüllte Kreis selber keinen Zustand darstellt.

Abb. 2.4. Zustandsdiagramm mit Standardzustand

Ein weiterer Mechanismus, um den nächsten Zustand anzugeben, ist der sogenannte *History-*Zustand. Mit Hilfe dieses Konstrukts ist es möglich, in den letzten Unterzustand zurückzukehren, der aktiv war, bevor der Superzustand verlassen wurde. Der *History-*Mechanismus wird durch den Buchstaben H in einem Kreis dargestellt. Um den aktiven Zustand für den ersten Wechsel in einen Superzustand zu kennzeichnen, wird der *History-*Mechanismus oft mit einem Standardzustand kombiniert. Abb. 2.5 zeigt ein Beispiel.

Das Verhalten des endlichen Automaten hat sich nun verändert: Sei der Automat zunächst im Zustand Z, und es ereigne sich die Eingabe m. Dann ist A der nächste Zustand, wenn der Superzustand S zum ersten Mal betreten wird. Ansonsten wird der zuletzt aktive Unterzustand betreten. Dieser Mechanismus hat viele Anwendungen. Wenn z.B. die Eingabe k eine Ausnahme darstellt, könnte die Eingabe m verwendet werden, um in den Zustand vor der Ausnahme zurückzukehren. Die Zustände A, B, C, D und E könnten Zustand Z auch wie eine Prozedur aufrufen. Nachdem diese "Prozedur" Z abgearbeitet ist, kehrt der Automat zum aufrufenden Zustand zurück.

Abb. 2.5. Zustandsdiagramm mit History-Mechanismus und Standardzustand

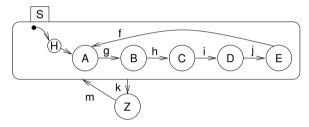

Der Automat aus Abb. 2.5 kann auch wie in Abb. 2.6 dargestellt werden. In diesem Fall wurden die Darstellungen für den Standardzustand und den *History*-Mechanismus kombiniert.

Abb. 2.6. Kombination der Symbole für History- und Standardzustand

Eine Spezifikationstechnik muss auch in der Lage sein, Nebenläufigkeit und Parallelität darzustellen. Zu diesem Zweck gibt es in StateCharts eine zweite Art von Superzuständen, die sogenannten UND-Superzustände.

**Definition:** Superzustände S heißen **UND-Superzustände**, wenn das System, das S enthält, sich in allen Unterzuständen von S gleichzeitig befindet, solange es sich in S befindet.

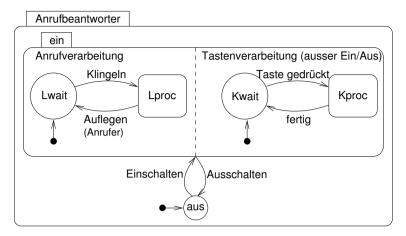

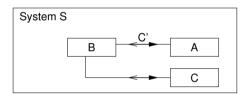

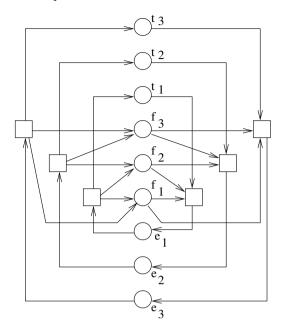

Das Diagramm für einen Anrufbeantworter in Abb. 2.7 enthält einen UND-Superzustand.

Ein Anrufbeantworter muss normalerweise zwei Aufgaben parallel ausführen: er wartet auf ankommende Anrufe und überprüft gleichzeitig, ob der Benutzer etwas auf den Eingabetasten eingegeben hat. In Abb. 2.7 heißen die entsprechenden Zustände Lwait und Kwait. Ankommende Anrufe werden im Zustand Lproc abgearbeitet, während Reaktionen auf die Eingabetasten im Zustand Kproc erzeugt werden. Der Ein-/Aus-Schalter wird fürs Erste so modelliert, dass die von ihm erzeugten Ereignisse (Einschalten und Ausschalten) separat dekodiert werden und somit nicht in den Zustand Kproc gewechselt wird. Wird der Anrufbeantworter ausgeschaltet, so werden die beiden im ein-Zustand enthaltenen Zustände verlassen. Sie werden erst wieder betreten, wenn der Anrufbeantworter wieder eingeschaltet wird. Zu diesem Zeitpunkt werden dann die

Abb. 2.7. Anrufbeantworter

Standardzustände Lwait und Kwait betreten. Solange die Maschine eingeschaltet ist, befindet sie sich immer in den beiden Unterzuständen des Zustands ein.

Für UND-Superzustände können die Unterzustände, die als Reaktion auf ein Ereignis betreten werden, unabhängig voneinander beschrieben werden. Jede beliebige Kombination von *History*-, Standardzuständen und expliziten Transitionen ist möglich. Für das Verständnis von StateCharts ist es wichtig zu begreifen, dass immer alle Unterzustände betreten werden, auch wenn es nur eine einzige explizite Transition zu einem der Unterzustände gibt. Analog dazu gilt, dass eine Transition aus einem UND-Superzustand heraus immer dazu führt, dass alle seine Unterzustände verlassen werden.

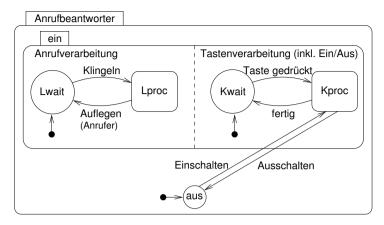

Als Beispiel modifizieren wir unseren Anrufbeantworter so, dass der Ein-/Aus-Schalter wie alle anderen Bedientasten im Zustand Kproc dekodiert und behandelt wird (s. Abb. 2.8).

Wenn der Anrufbeantworter ausgeschaltet wird, findet eine Transition in den aus-Zustand statt. Dieser Übergang führt dazu, dass auch der Zustand, der auf ankommende Anrufe wartet, verlassen wird. Das Wiedereinschalten der Maschine führt dazu, dass eben dieser Zustand auch wieder mit betreten wird.

Zusammenfassend können wir festhalten: Zustände in StateCharts-Diagrammen sind entweder UND-Superzustände, ODER-Superzustände oder Basiszustände.

Abb. 2.8. Anrufbeantworter mit veränderter Ein-/Ausschalter-Modellierung

#### 2.3.2 Zeitbedingungen

Da es notwendig ist, in eingebetteten Systemen Zeitbedingungen zu modellieren, bietet StateCharts die sogenannten *Timer* an. Zeitbedingungen werden durch das gezackte Symbol im linken Teil von Abb. 2.9 dargestellt.

Abb. 2.9. Zeitbedingungen in StateCharts

Wenn das System für die im *Timer* angegebene Zeitdauer im *Timer*-Zustand war, wird ein *Time-Out* ausgelöst und das System verlässt diesen Zustand. *Timer* können auch hierarchisch verwendet werden.

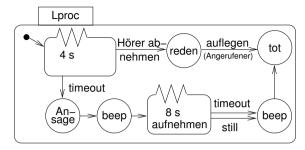

Ein *Timer* könnte beispielsweise in einer tieferen Hierarchiestufe des Anrufbeantworters verwendet werden, um das Verhalten des Zustands Lproc zu beschreiben. Abb. 2.10 zeigt eine mögliche Beschreibung für diesen Zustand.

Da das Auflegen des Anrufers in Abb. 2.7 in Form einer Ausnahmebehandlung realisiert ist, wird der Zustand Lproc immer erst dann verlassen, wenn der Anrufer auflegt. Wenn allerdings der Angerufene auflegt, hat der Entwurf des Zustands Lproc einen Schönheitsfehler: wenn der Angerufene zuerst auflegt, ist das Telefon solange tot (und still), bis der Anrufer ebenfalls aufgelegt hat.

StateCharts beinhalten noch weitere Sprachelemente, die beispielsweise im Buch von Harel [Harel, 1987] zu finden sind. Zusammen mit Drusinsky gibt

Abb. 2.10. Behandlung von eingehenden Anrufen in Lproc

Harel [Drusinsky und Harel, 1989] in einem Artikel eine genauere Beschreibung der Semantik von StateMate, einer StateCharts-Implementierung.

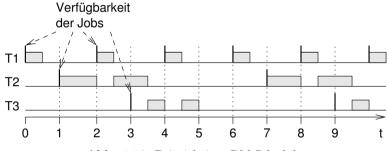

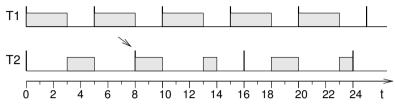

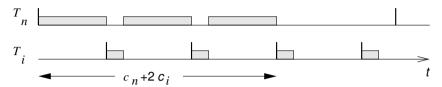

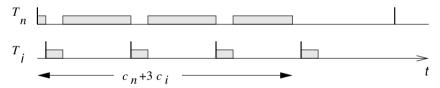

## 2.3.3 Kantenbeschriftungen und StateMate-Semantik